Question

In: Computer Science

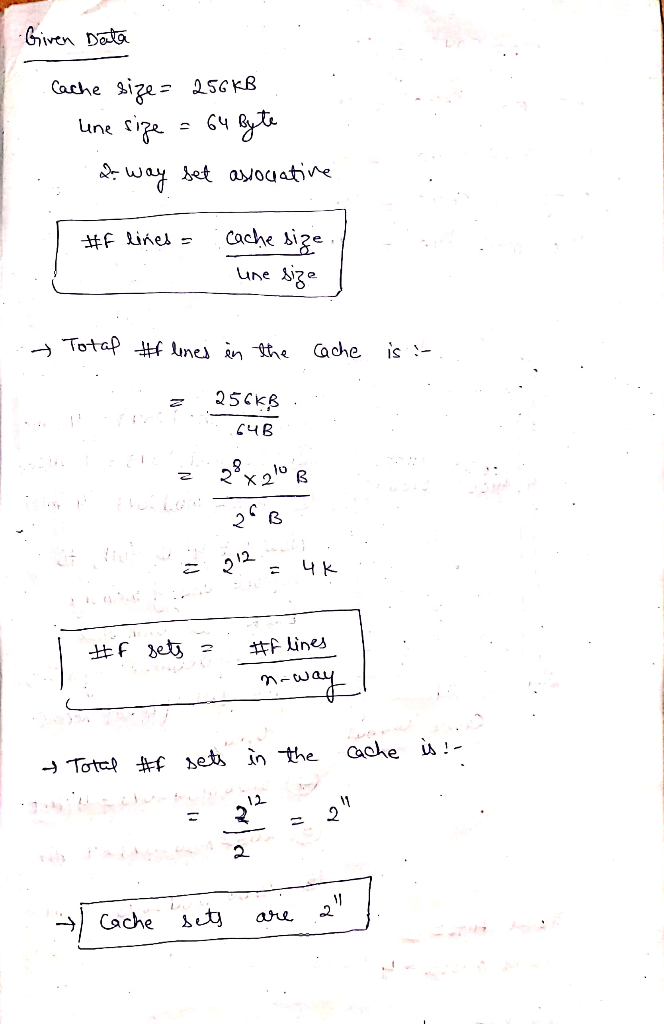

Assume that the cache size is 256kB, and each cache line is 64 Bytes. (10%) Let...

- Assume that the cache size is 256kB, and each cache line is 64 Bytes. (10%)

- Let us assume this is a Two-way associative cache. How many cache sets are there?

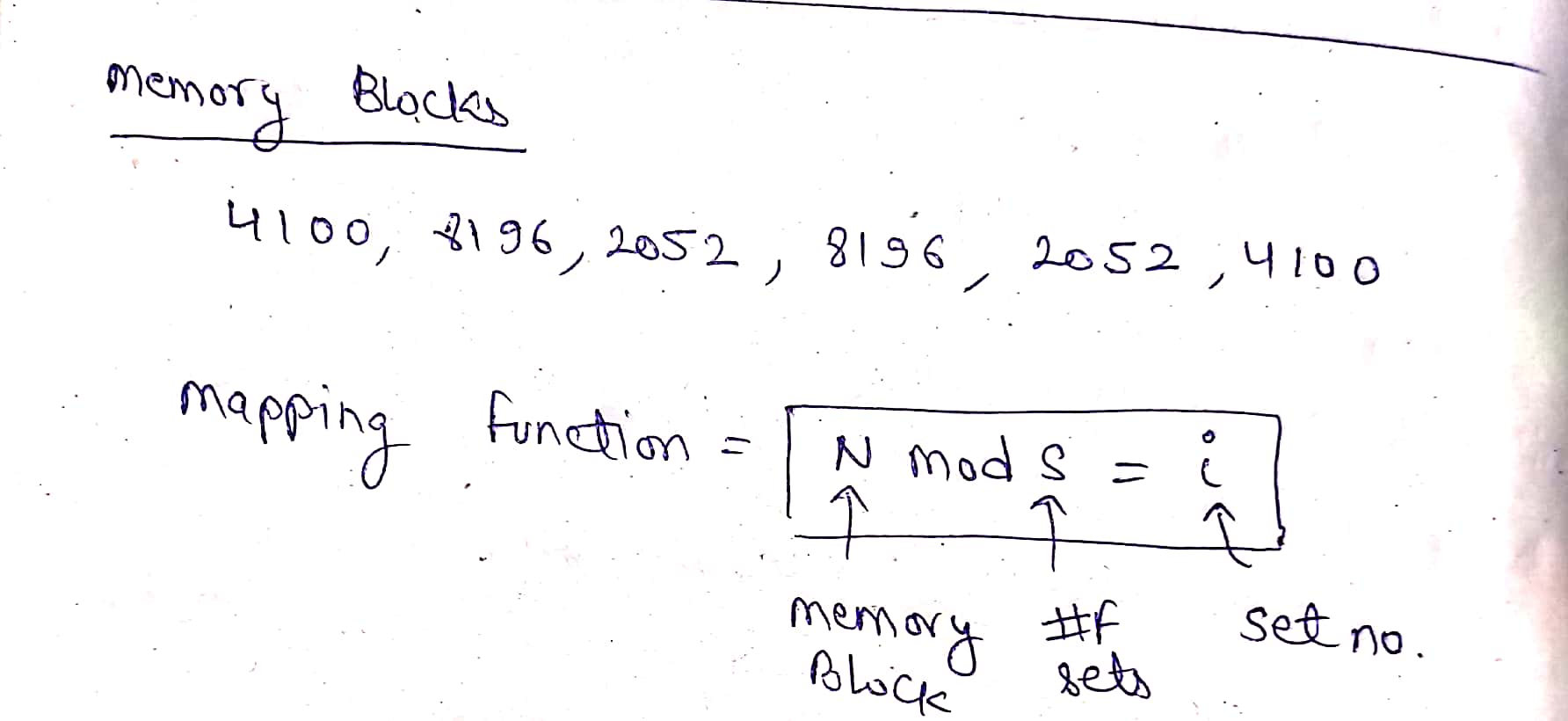

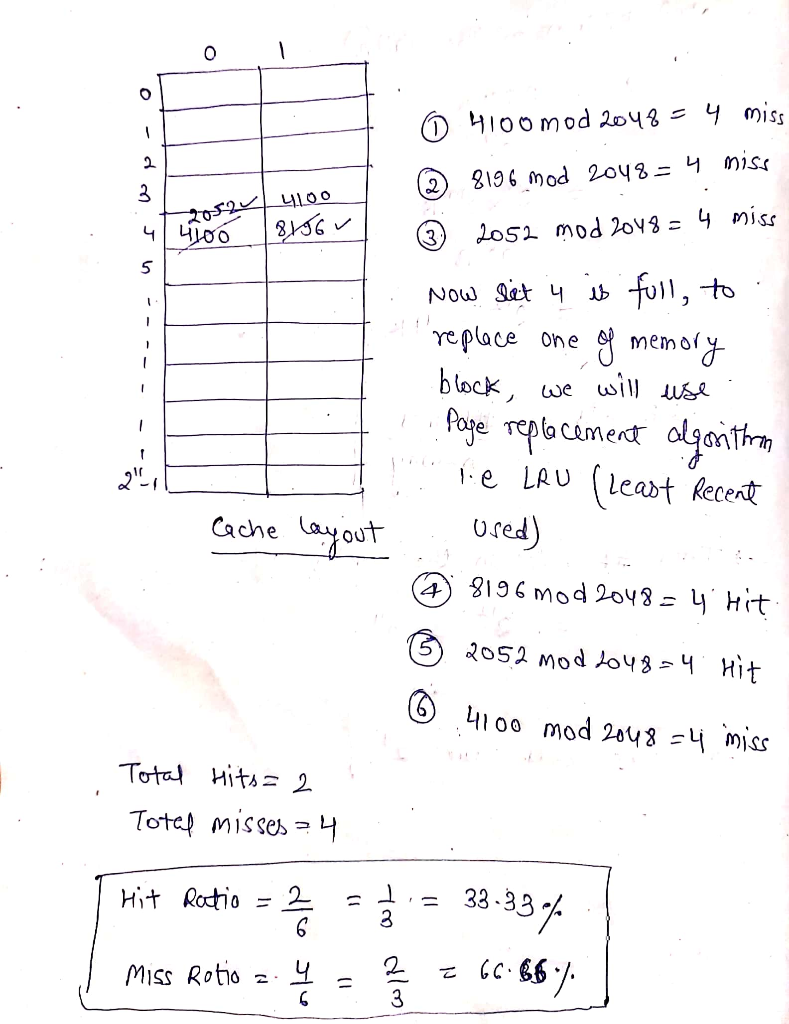

- Let us assume the following memory blocks need to be accessed:

Memory Blocks #4100, 8196, 2052, 8196, 2052, 4100

If the cache is initially empty, what is the cache hit/miss rate?

Solutions

Expert Solution

Summary:-

For memory block replacement, we are using LRU ( least recent used). To map any memory block to set, we are using mapping function. For clear explanation please refer to the image.

Related Solutions

Assume a computer with a cache that holds 64 bytes and has a block size of...

Assume a computer with a cache that holds 64 bytes and has a

block size of 32 bytes. Direct address mapping is used and from the

beginning the cache is empty. The following program sequence is

executed:

for (col = 0; col < 2; col++) {

for (row = 0; row < 4; row++)

A[row][col] = B[row] * C[col]; }

Assume that for the variables row and col registers are

used.

The matrix A consists of 4 rows and 4...

Computer archieture 1. Assume that the cache size is 512kB, and each cache line is 128...

Computer archieture

1. Assume that the cache size is 512kB, and

each cache line is 128 Bytes.

If it’s a 4-way associative cache, how many sets are there? If

it’s a 2-way associative cache, how many sets are there?

Let’s assume the cache is initially empty, and LRU policy is

used for cache line replacement. If the following memory blocks are

accessed:

Mem-block # 7, 1031, 2055, 4103, 1031,

7, 2055, 3079, 1031, 3079

What is the cache hit/miss rate...

A direct mapped cache has 16 blocks and block size is 64-bits (8 bytes). a. Where...

A direct mapped cache has 16 blocks and block size is 64-bits (8

bytes).

a. Where will the memory block 45 reside in cache? (5

b. Where will be the memory address 1667 mapped in cache

Consider a 4-way set-associative cache, 4 rows, a line size of 128 bytes and a write-back...

Consider a 4-way set-associative cache, 4 rows, a line size of

128 bytes and a write-back policy. The following requests are made

to memory:

Load: 0b0011111001000101

Load: 0b1000111110110100

Load: 0b0110101111110100

Store: 0b0010110000000110

Store: 0b1111001001110101

Store: 0b1110000111000001

Load: 0b0000000010100110

Load: 0b0101001001001101

Assuming the machine is in cold-start, profile the contents to the

cache after all of the requests have been made. State any

assumption you make (if needed).

Assume a byte-addressable memory has 64K bytes. Blocks are 8 bytes in length and the cache...

Assume a byte-addressable memory has 64K bytes. Blocks

are 8 bytes in length and the cache consists of 4K bytes. Show the

format for a main memory address assuming a 4-way set associative

cache mapping scheme. Include the field names as well as their

sizes.

A direct mapped cache has 32 cache lines.Each cache line consists of 4 words, and each...

A direct mapped cache has 32 cache

lines.Each cache line consists of 4 words, and each word is four

bytes.The address bus consists of 16 bits.

How many bits are required for the

tag in this direct-mapped cache?

Suppose a computer using direct mapped cache has 232 bytes of main memory and a cache...

Suppose a computer using direct mapped cache has 232

bytes of main memory and a cache of 1024 blocks, where each block

contains 32 bytes.

[2] How many blocks of main memory does this computer

have?

[4] Show the format of a memory address as seen by cache; be

sure to include the field names as well as their sizes.

[3] Given the memory address 0x00001328, to which cache block

will this address map? (Give you answer in decimal.)

A...

Below are listed parameters for different direct-mapped cache designs. Cache Data Size: 32 KiB Cache Block...

Below are listed parameters for different direct-mapped cache

designs.

Cache Data Size: 32 KiB

Cache Block Size: 2 words

Cache Access Time: 1 cycle

Word: 4 bytes.

Calculate the total number of bits required for the cache listed

above, assuming a 32-bit address. Given that total size, find the

total size of the closest direct-mapped cache with 16-word blocks

of equal size or greater. Explain why the second cache, despite its

larger data size, might provide slower performance than the...

Suppose a computer using direct mapped cache has 224 bytes of byte-addressable main memory, and a...

Suppose a computer using direct mapped cache has 224

bytes of byte-addressable main memory, and a cache of 128 blocks,

where each cache block contains 8 bytes. For fully associative

cache, to which block of cache the address 0x189B5A maps?

Group of answer choices

Block 6

Block 75

Not enough information

Block 10

a) consider a direct mapped cache with 10 blocks of 10 words each. Suppose main memory...

a) consider a direct mapped cache with 10 blocks of 10 words

each. Suppose main memory is 1000 words. For ewach memory address

below say what cache block it maps to, what is the offset, and what

is the tag.

934, 666, 348, 522

ADVERTISEMENT

ADVERTISEMENT

Latest Questions

- Use Matlab GUIDE to create a program with graphic user interfac(GUI). The program is designed to...

- The new market equilibrium price and the new market equilibrium quantity is as follows Dx =...

- a) What are the different types of “light” (electromagnetic waves), starting from radio waves? Why do...

- I would like to see a java language example using classes customer() and animal() which get...

- Hi-Tek Manufacturing, Inc., makes two types of industrial component parts—the B300 and the T500. An absorption...

- A 1.8-cm-tall object is 28cm to the left of a lens with a focal length of 14cm...

- 7.15 Translate the following string method invocations to functions calls in namespace str: (Python) (a) '...

ADVERTISEMENT

venereology answered 2 months ago

venereology answered 2 months ago